|

5

BAB II

LANDASAN TEORI

2.1

AVR

AVR merupakan kepanjangan dari Advanced Virtual RISC (wikipedia).

Arsitektur internalnya dirancang oleh 2 orang: Alf-Egil Bogen dan Vegard Wollen, pada

Institut Teknologi Norwegia (NTH), dan kemudian dikembangkan oleh Atmel Norwegia.

AVR

merupakan salah

satu

peralatan

RISC.

RISC

merupakan singkatan

dari

“Reduced Instruction Set Computing” yang artinya peralatan ini didesain untuk berjalan

dengan sangat cepat dengan menggunakan sejumlah instruksi yang

lebih sedikit. Jumlah

instruksi

yang

lebih

sedikit

inilah

yang

menyebabkan

peralatan

RISC berjalan

lebih

cepat, karena berdasarkan faktanya, dengan jumlah instruksi mesin yang terbatas, semua

instruksinya dapat dijalankan

hanya dalam satu clock

saja.

Artinya prosesor AVR yang

menggunakan clock 16 MHz dapat mengeksekusi hampir 16 juta instruksi perdetik.

Secara

keseluruhan arsitektur

dari

Atmel

AVR

menyerupai

sebuah

mikrokomputer. AVR

sudah

memiliki sendiri

sebuah

CPU,

memory,

dan

bagian

I/O.

Bagian

CPU

memang tidak

dapat kita ketahui

bagaimana cara

kerjanya. Tapi

memory

dan bagian I/O dapat dilihat dengan jelas dan perlu kita pahami dengan baik jika

ingin

mendesain aplikasi dengan menggunakan AVR.

Untuk

memaksimalkan kinerja

dan

paralelisme,

AVR

menggunakan

arsitektur

Harvard,

yaitu

menggunakan

memory

dan

bus

yang

berbeda

untuk

program dan data.

Instruksi pada memory program dijalankan dengan menggunakan pipeline tunggal.

Ketika satu instruksi sedang dieksekusi, instruksi berikutnya sudah di prefetch ke dalam

|

|

6

memory program. Konsep

ini

memungkinkan

instruksi dieksekusi dalam setiap clock.

Memory program yang digunakan dalam AVR adalah Flash Memory.

Register file yang digunakan dalam AVR adalah register umum 32 x 8 bit dengan

waktu akses satu clock. Dengan

menggunakan ini, operasi ALU dapat dilakukan dalam

satu

clock.

Dalam

operasi

ALU yang

biasa,

dua operand

didapat

dari keluaran

file

register, operasi kemudian dijalankan, dan

hasilnya kemudian disimpan

lagi

dalam file

register- semuanya dilakukan dalam satu siklus clock.

Enam dari 32 register yang ada dapat digunakan sebagai indirect address register

pointer 16 bit untuk pengalamatan data space, yang memungkinkan penghitungan alamat

yang

efisien.

Satu

dari

pointer

alamat

ini juga

dapat

digunakan sebagai

pointer

alamat

untuk

look

up table

pada

Flash

memory.

Selain

itu

juga

ada 3

register tambahan pada

AVR ini, yaitu register x, y, dan z, yang masing-masing sebesar 16 bit.

ALU

yang

digunakan mendukung

operasi

aritmatika dan

logika

antar

register

ataupun

antara

sebuah

konstanta

dan

sebuah

register.

Operasi

dengan

register

tunggal

juga dapat dieksekusi di ALU. Setelah suatu operasi aritmatika dijalankan, status register

diupdate untuk menyimpan informasi tentang hasil operasi yang baru saja dilakukan.

Aliran program dilakukan dengan menggunakan instruksi call dan jump bersyarat

ataupun tak bersyarat, mampu secara langsung mengalamati seluruh alamat yang tersedia.

Kebanyakan

instruksi

AVR memiliki

format

16 bit.

Setiap

alamat

memory

program

terdiri dari instruksi 16 atau 32 bit.

Flash memory yang digunakan dibagi menjadi 2 bagian, yaitu bagian boot

program dan bagian program aplikasi. Masing-masing bagian memiliki proteksi lock bit

|

7

tersendiri

untuk proses baca dan baca/tulis.

Instruksi SPM yang menulis

ke bagian

program aplikasi harus disimpan di bagian boot program.

Selama pemanggilan interupt

dan

subrutin,

alamat

kembali

pada

PC

(Program

Counter) disimpan

ke

dalam

stack.

Stack

ini

terletak pada

data

umum di SRAM,

dan

konsekuensinya

ukuran

stack

hanya dibatasi

oleh

ukuran

total SRAM dan

penggunaan

SRAM. Semua program harus menginisialisasi SP dalam reset routine (sebelum subrutin

atau interupt dieksekusi). Stack Pointer dapat diakses dengan baca/tulis pada bagian I/O.

Data

pada

SRAM

dapat

diakses dengan mudah

melalui

lima

metode

pengalamatan

berbeda

yang

didukung oleh

arsitektur AVR.

Ruang

memory

dalam

arsitektur AVR

semuanya bersifat linear dan memiliki peta memory yang umum.

2.2

AT Mega 8535

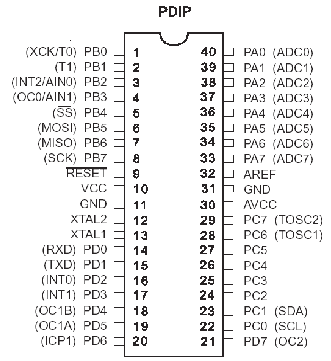

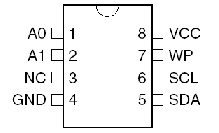

Gambar 2.1 Konfigurasi pin AT Mega 8535

|

|

8

Deskripsi pin :

V

cc

Digital Supply Voltage

Gnd

Ground

Port A (PA7..PA0)

Port A digunakan sebagai masukan analog untuk ADC

Port B (PB7..PB0) Port B adalah sebuah port I/O dua arah 8 bit, dengan resistor pull

up internal.

Port C (PC7..PC0) Port C mempunyai fungsi yang sama dengan Port B, yaitu sebagai

port I/O dua arah 8 bit, dengan resistor pull up internal

Port D (PD7..PD0) Port D mempunyai fungsi yang sama dengan Port B, yaitu sebagai

port I/O dua arah 8 bit, dengan resistor pull up internal. Selain itu

port D juga digunakan untuk fitur-fitur khusus

yang tersedia pada

AT mega 8535

Reset

Untuk mereset masukan. Jika pin ini mendapat masukan low

maka

pin ini akan mengeluarkan reset, bahkan jika tidak mendapat clock.

XTAL 1 Masukan

untuk

penguat

osilator

inverting

dan

juga sebagai

masukan bagi clock internal AVR

XTAL 2

Keluaran dari penguat osilator inverting

AVCC

AVCC adalah pin supply tegangan untuk port A dan ADC. Pin ini

harus dihubungkan secara eksternal dengan pin VCC, bahkan jika

ADC

tidak

digunakan. Jika

ADC

digunakan, pin

ini

harus

dihubungkan ke VCC melalui sebuah Low Pass Filter

AREF

AREF adalah pin reference analog untuk ADC

|

|

9

ATMega 8535 adalah

mikrokontroler CMOS

8

bit

berdaya rendah

yang dibuat

berdasarkan

arsitektur

RISC

AVR.

Dengan

mengeksekusi instruksi dalam

satu

clock,

ATMega 8535 mempunyai kemampuan mendekati 1 MIPS per MHz sehingga perancang

sistem dapat mengoptimalkan antara konsumsi daya dan kecepatan pemrosesan.

Inti

dari

AVR

mengkombinasikan satu

set

instruksi

yang

beragam

dengan

32

register

umum.

Semua

register

ini

dihubungkan secara

langsung ke

ALU

(Arithmetic

Logic

Unit),

sehingga

dua

register

yang

terpisah

dapat

diakses

dalam

satu

instruksi

tunggal dan dieksekusi dalam satu siklus clock. Hasil dari arsitektur ini adalah kode yang

lebih

efisien

tapi

dengan

hasil

yang

10

kali

lebih

cepat

daripada

mikrokontroler CISC

konvensional.

ATMega 8535

menyediakan fitur-fitur sebagai berikut: 8 Kbytes ISP flash

memory dengan kemampuan baca sambil menulis (read while write), 512 byte EEPROM,

512 byte SRAM, 32 jalur I/O, 32 register umum, 3 timer/counter fleksibel, dengan mode

pembandingan,

interupt

internal

dan eksternal,

USART, 2 wire serial

interface

berorientasi byte,

ADC

10 bit

dengan 8 channel dengan masukan diferensial

(optional)

dengan gain yang dapat diprogram di paket TQFP, watchdog timer yang dapat diprogram

dengan

osilator

internal,

port

serial

SPI,

dan

6

mode

penghematan

daya

yang

dapat

dipilih.

Mode idle akan menghentikan CPU tetapi dengan SRAM, timer/counter, port SPI

dan sistem interupt tetap bekerja. Mode power down akan menyimpan nilai register tetapi

membuat osilator berhenti bekerja, dan mematikan semua fungsi lain CPU sampai

interupt

berikutnya atau

terjadi

reset

secara

hardware.

Pada

mode

power

save

timer

asinkron akan terus bekerja, sehingga pemakai masih dapat

memanfaatkan timer

|

|

10

sementara perangkat

lainnya

dalam

keadaan

tidur.

Mode

ADC

noise

reduction

menghentikan CPU

dan

semua

modul

I/O

kecuali

timer

asinkron

dan

ADC,

untuk

meminimalkan noise selama proses

pengkonversian ADC. Pada

mode standby, osilator

kristal

akan terus berjalan

sementara perangkat

lainnnya tidur.

Mode

ini

menghasilkan

start up

yang sangat cepat dengan konsumsi daya rendah. Pada mode extended standby,

baik osilator maupun timer asinkron masih terus berjalan.

Perangkat

ini

dirancang

dengan

menggunakan teknologi

memory

nonvolatile

berkepadatan tinggi

milik

Atmel.

Dengan

adanya

on-chip

ISP

Flash

memungkinkan

memory

program

dapat diprogram

ulang

secara

in-system

melalui

interface serial

SPI,

dengan pemrogram memory nonvolatile konvensional, atau dengan program on-boot chip

yang

berjalan pada

inti

AVR. Boot program bisa

menggunakan interface apapun

untuk

mendownload program

aplikasi

ke

dalam bagian aplikasi

dari

flash

memory.

Software

pada bagian boot flash masih akan terus berjalan walaupun bagian aplikasi flash sedang

diupdate, sehingga menyediakan operasi baca sambil menulis (read while write). Dengan

mengkombinasikan CPU

RISC

8

bit dengan

in-system

self-programmable

flash dalam

satu chip tunggal, Atmel ATMega 8535 adalah mikrokontroler ampuh yang menyediakan

sebuah

solusi

yang

fleksibel dengan

harga

yang

efektif

untuk

banyak

aplikasi

sistem

embedded.

ATMega 8535 juga didukung dengan serangkaian program dan development tool

yang

meliputi:

compiler

C,

macro

assembler,

program

debugger/simulator, in

circuit

emulator, dan juga evaluation kits.

|

|

11

2.3 Komunikasi serial menggunakan SPI

SPI (Serial Peripheral Interface) adalah salah satu bentuk komunikasi serial yang

disediakan dalam

AVR sehingga

memang

direkomendasikan menggunakan SPI

karena

dari datasheet. SPI

merupakan sebuah bus komunikasi serial sinkron, artinya transmitter

dan

receiver

yang

terlibat dalam komunikasi SPI harus

menggunakan clock yang

sama

untuk

mensinkronkan

pendeteksian

bit

pada

receiver.

Normalnya

bus

SPI

digunakan

untuk

komunikasi

dengan

jarak

yang

sangat

pendek

dengan

perangkat atau

mikrokontroler lain yang terletak pada papan rangkaian yang sama atau setidaknya dalam

hardware

yang sama.

Ini berbeda

dari

UART,

yang digunakan

untuk

komunikasi pada

jarak

yang

lebih

jauh,

seperti

antara

sebuah

mikrokontroler dan

PC.

Bus

SPI

dikembangkan untuk

menyediakan bentuk

komunikasi

yang

memiliki

kecepatan

yang

relatif tinggi pada jarak dekat dengan menggunakan jumlah pin kontroler yang minimum.

Komunikasi SPI terdiri dari sebuah master dan slave. Keduanya mengirim dan menerima

data

secara

simultan,

tapi

master

adalah

yang

bertanggung jawab

untuk

menyediakan

sinyal

clock

untuk

proses

transfer

data.

Dengan

cara

ini

masterlah

yang

mengatur

kecepatan transfer data, dan karenanya, adalah yang mengendalikan transfer data.

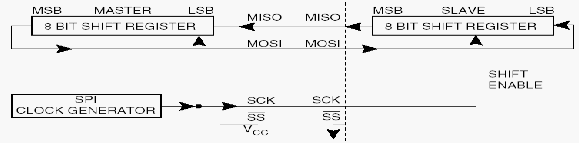

Gambar

di

bawah

menunjukkan koneksi

antara

unit

master

dan

slave

dalam

komunikasi SPI. Master menyediakan clock dan data 8 bit, yang dikirimkan ke pin MOSI

(master out slave in) pada master. Data 8 bit yang sama dikirim ke unit slave, satu bit per

pulsa clock ke pin MOSI pada slave. Ketika 8 bit data dikirim keluar dari master ke slave,

8

bit data juga dikirim dari slave ke masternya melalu pin MISO (master in slave out) ke

pin

MISO

pada

master.

Karena

itu

komunikasi SPI

pada

dasarnya

adalah

berbentuk

melingkar di

mana 8

bit data mengalir dari

master ke

slave dan

himpunan 8 bit yang

|

12

berbeda

mengalir dari

slave ke master. Dengan cara ini

master dan

slave dapat saling

bertukar data dalam satu komunikasi tunggal.

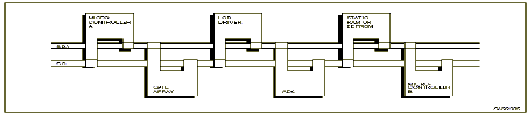

Gambar 2.2 Koneksi unit Master dan Slave

Adalah

sangat

memungkinkan untuk

menghubungkan beberapa

perangkat

sekaligus

menggunakan bus

SPI,

karena

semua

pin

MOSI

dan

pin

MISO

dapat

disambungkan

sekaligus.

Perangkat

manapun

dalam

jaringan

ini

dapat

menjadi

master

hanya dengan

memutuskan

untuk

mengirimkan data.

Sebuah perangkat dalam

jaringan

ini dapat

menjadi slave ketika

pin

SS(slave

select)

digroundkan.

Biasanya

pin SS

dari

para slave

ini

dihubungkan entah

dengan port

paralel

pada

master

atau

dengan

sebuah

decoder yang akan menentukan perangkat mana yang akan menjadi slave.

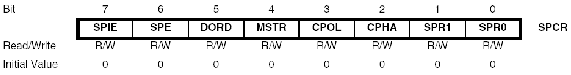

SPCR

(SPI

control

register)

mengendalikan operasi pada

interface SPI.

Definisi

bit pada SPCR ditunjukkan pada gambar di bawah. Dalam cara yang sama dengan control

register yang telah dibahas di atas, ada

bit

yang digunakan

untuk mengenable

interface

SPI

dan

interup

yang

berhubungan dengan

SPI,

dan

ada

bit

yang

digunakan

untuk

mengendalikan kecepatan komunikasi. Juga

ada

bit

yang

digunakan

untuk

menentukan

perangkat mana yang bertindak sebagai master, MSTR.

|

13

Tambahan pula, ada bit yang digunakan untuk mengatur urutan pengiriman data,

MSB first atau LSB first, dan ada juga bit yang digunakan untuk mengatur polaritas clock

dan fase clock. Ada juga bit yang digunakan untuk mencocokkan

antara peralatan

komunikasi SPI dengan perangkat SPI lainnya.

Gambar 2.3 Definisi bit SPCR

•

Bit 7 SPIE (SPI interupt enable): bit ini

menyebabkan interupt SPI dijalankan

jika bit SPIF pada register SPSR diset dan jika bit Global Interupt Enable pada

SREG juga di set

•

Bit

6

SPE

(SPI enable): ketika

bit

SPE bernilai

1, SPI enable.

Bit

ini

harus

diset jika ingin menjalankan semua operasi SPI.

•

Bit 5 DORD (Data order): ketika bit DORD bernilai 1, maka bagian LSB data

akan dikirim terlebih dahulu. Ketika bit DORD bernilai 0,

maka bagian MSB

data akan dikirim terlebih dahulu.

•

Bit

4

MSTR (Master/ Slave

Select): bit

ini

akan

memilih

mode

SPI

Master

jika bernilai 1, dan mode SPI Slave jika bernilai 0.

•

Bit

3

CPOL (Clock polarity): ketika bit

ini

bernilai satu,

SCD

akan bernilai

high

ketika sedang idle.

Ketika CPOL

bernilai nol,

SCK

akan bernilai low

ketika idle. Fungsionalitas CPOL dirangkum sebagai berikut.

|

14

Table 2.1 Fungsionalitas CPOL

•

Bit

2

CPHA (Clock phase):

settingan

pada

CPHA

akan

menentukan apakah

data diambil pada sisi awal (leading edge) atau sisi akhir (trailing edge) dari

SCK. Fungsionalitas dari CPHA dirangkum sebagai berikut.

Table 2.2 Fungsionalitas CPHA

•

Bit 1, 0 SPR1 dan SPR0 (SPI clock

rate select

1 dan 0): kedua

bit ini

mengatur

kecepatan

SCK

dari

perangkat

yang

diatur

sebagai

master.

SPR1

dan

SPR0

tidak

mempunyai efek

pada

slave.

Hubungan

antara

SCK

dan

frekuensi clock osilator f

osc

ditunjukkan pada tabel di bawah ini.

Table 2.3 Hubungan antara SCK dan frekuensi osilator

|

15

2.4

Komunikasi menggunakan I2C

I

2©

merupakan

standar

komunikasi

dengan

menggunakan 2

kabel

dengan

kecepatan yang

cukup

tinggi

maka

antara

IC

yang

satu

dengan

yang

lainnya

dapat

berkomunikasi dengan baik. Dengan memanfaatkan jalur bus dan address yang bervariasi

maka I

2©

mampu mengalamati banyak device. I²

C

terdiri dari beberapa bagian yaitu :

1. Transmitter: bagian yang berfungsi mengirimkan data ke Bus

2. Receiver: bagian yang menerima data dari Bus

3.

Master:

bagian

yang

melakukan

transfer,

mengenerate Clock

dan

membatalkan transfer data

4. Slave: bagian yang ditunjuk oleh master sebagai tempat yang dituju.

5.

Multi–Master:

lebih

dari

satu

master

dapat

mengontrol Bus

dalam

waktu

bersamaan tanpa membuat corrupt pada data yang ada.

6. Arbitration: Prosedur

yang menentukan/membatasi Multi Master dan

membuat hanya satu dari dua master yang dapat mengatur Bus sehingga tidak

terjadi Corrrupt pada data.

7. Synchronization: prosedur

yang

mencocokkan

antara

Sinyal Clock dan

beberapa device.

Gambar 2.4 Konfigurasi I2C dengan lebih dari 2 device

|

16

Pada

gambar

2.4

komunikasi antara 2

mikrokontroller A dan

mikrokontroller B

dan

device-device lainnya

(Gate

Array,

LCD

Driver,

ADC,

Static

RAM/

EEPROM)

dilakukan

dengan

menggunakan 2 jalur

(SDA

dan

SCL).

SDA

merupakan

Serial

Data

Line

yang merupakan jalur

untuk

mengirimkan data-data secara serial. Sedangkan SCL

merupakan Serial Clock

Line yang berfungsi

untuk

mengirimkan Clock

yang berfungsi

untuk sinkronisasi

dan

menandakan

pengiriman

paket-paket

data.

Berikut

merupakan

timing diagram dari I²

C

(Gambar 2.5).

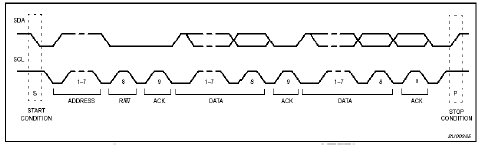

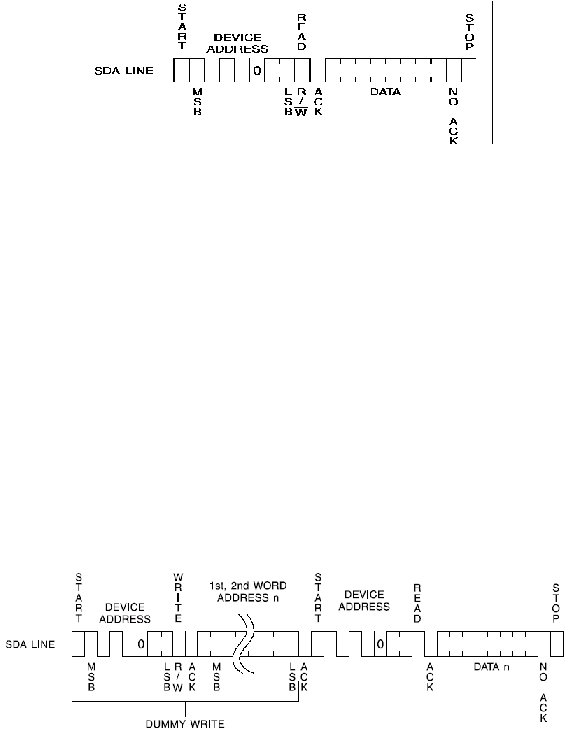

Gambar 2.5 Timing diagram dari I2C

Komunikasi

antar

IC

dengan

menggunakan metode

I

2©

harus

memperhatikan

beberapa hal antara lainnya pada awal SDA

mengirimkan transisi data dari high ke

low

(“falling edge”) sedangkan SCL harus berada pada kondisi high. Kondisi ini menandakan

mulainya

pengiriman

data

(“start

condition”). Selanjutnya pengiriman

address

yang

ditandakan dengan

SCL

yang akan

mengirimkan transisi

data

dari

high ke

low

dan

ke

high lagi. Selanjutnya pengiriman status untuk menulis atau membaca data yang ditandai

dengan tansisi data SCL dari

low ke high. Setelah mendapatkan ack dari IC tujuan yang

ditandai dengan satu clock penuh pada SCL, maka data akan dapat dikirimkan menuju IC

tujuan

dengan

transisi SCL

dari

low

ke

high

(“rising

edge”)

,

ACK

dapat

diartikan

|

17

sebagai

penanda

ketika

data

berhasil

diterima

oleh

IC

tujuan.

“Stop

condition” atau

penanda bahwa

semua

data

telah dikirimkan, ditandai dengan perubahan SDA

dari

low

ke high (“rising edge”) yang diikuti dengan logic high pada SCL. Berikut ini merupakan

paket-paket data yang digunakan dalam komunikasi I

2C

(Gambar 3.3):

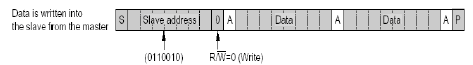

Gambar 2.6 Paket data untuk melakukan penulisan menuju slave

Untuk

melakukan penulisan dari

master

menuju ke

slave device maka beberapa

paket data dibutuhkan untuk melakukan proses tersebut antara lainnya: start bit, address,

R/W, ACK, Data yang hendak dikirimkan, ACK dan pengiriman data yang selanjutnya,

ACK dan stop bit. Untuk perintah R/W

master device harus

menunggu ACK dari slave

device

yang

menandakan bahwa

perintah

R/W

berhasil

diterima

dan

di

konfirmasi.

Demikian

juga

halnya

untuk

data

yang

dikirimkan

harus

menunggu

ACK

dari

slave

device jika pengiriman berhasil dilakukan maka ditandai dengan adanya ACK jika tidak

master device harus mengirimkan data tersebut kembali.

Sedangkan untuk

melakukan pembacaan yang

harus

dilakukan

ialah

hanya

mengganti perintah untuk pembacaan (logic high) setelah data pertama didapatkan maka

master

mengirimkan ACK ke slave device,

untuk data

yang selanjutnya

yang diterima,

master tidak

perlu

mengirimkan ACK. Istilah-istilah yang

digunakan dalam komunikasi

dengan menggunakan I2C :

|

18

•

Start Condition : menentukan kapan data tersebut mulai dikirim

•

?

Acknowledge :

untuk

memeriksa dan mencocokkan address yang akan

diterima

oleh

device

slave

dan

menentukan

bagianbagian dari

data

yang

dikirimkan dan memilah-milah sehingga tidak terjadi kesimpang siuran antara

address dan data yang dikirimkan

•

Stop Condition : kondisi yang menentukan suatu data selesai dikirim.

2.5

Pemrograman memory

AVR menyediakan beberapa cara untuk memprogram memory, yaitu secara

paralel, serial, maupun JTAG.

2.5.1

Pemrograman parallel

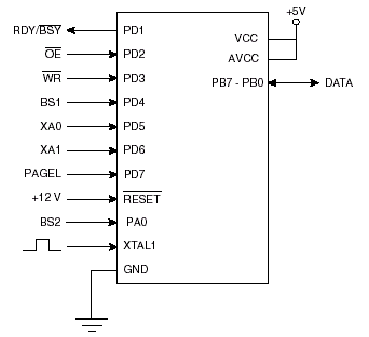

Gambar 2.7 Konfigurasi pin dalam pemrogaman paralel

|

19

Tabel 2.4 Pemetaan nama pin

Nama sinyal

Nama pin

I/O

Fungsi

RDY/BSY

PD1

O

0: alat sedang sibuk memprogram;

1: alat sudah siap untuk perintah baru

OE

PD2

I

Output Enable (active low)

WR

PD3

I

Write pulse (active low)

BS1

PD4

I

Byte select 1 (“0”

untuk byte low,

“1”

untuk byte

high)

XA0

PD5

I

XTAL action bit1

XA1

PD6

I

XTAL action bit 2

PAGEL

PD7

I

Page

load

untuk

memory

program

dan

data

EEPROM

BS2

PA0

I

Byte select 2 (“0”

untuk

low byte,

“1”

untuk

high

byte)

DATA

PB7-0

I/O

Bus data 2 arah (menjadi output ketika OE bernilai

low).

Untuk memasukimode pemrograman parallel, digunakan algoritma berikut :

1. Beri tegangan

sebesar

4,5-5,5

v

antara

Vcc

dan

GND,

dan

tunggu

setidaknya

selama 100 µs.

2. Beri

RESET

nilai

“0”,

tunggu setidaknya selama 100

ns dan aktifkan XTAL1

setidaknya 6 kali.

3. Set nilai pin prog_enable menjadi “0000” dan tunggu selama 100 ns.

|

|

20

4. Beri tegangan sebesar 11,5-12,5 v pada RESET. Aktifitas apapun yang dilakukan

pada pin prog_enable dalam 100 ns setelah pemberian tegangan 12

v

dilakukan

pada

RESET, akan menyebabkan kegagalan dalam memasuki mode

pemrograman paralel.

2.5.2

Pemrograman serial

Baik memory flash maupun EEPROM bisa diprogram dengan menggunakan jalur

serial SPI ketika RESET dihubungkan ke GND. Interface serial ini terdiri dari pin SCK,

MOSI (input),

dan MISO (output).

Setelah

RESET

diberi nilai low, instruksi

programming enable

harus

dieksekusi dahulu

sebelum

operasi

pemrograman/

penghapusan dapat dilakukan. Ketika menulis data serial ke

ATmega8535, data

diclock

pada rising edge dari SCK. Ketika membaca data serial dari ATmega8535, data diclock

pada falling edge dari SCK. Sistem ini menggunakan komunikasi SPI dengan algoritma

:

1. Beri daya antara Vcc dan

Ground ketika RESET dan SCK diset 0. Di beberapa

sistem,

programmer tidak bisa

menjamin bahwa

SCK

tetap bernilai

low

selama

proses

power-up.

Untuk

kasus

ini,

RESET harus

diberi

sinyal

pulsa

positif

setidaknya selama dua kali clock setelah SCK diset 0.

2.

Tunggu

setidaknya

selama

20

ms

dan

aktifkan

pemrograman serial

dengan

mengirimkan instruksi serial programming enable ke pin MOSI.

3.

Instruksi

pemrograman serial

tidak

akan

bekerja

jika

komunikasi

tidak

dalam

keadaan sinkron. Ketika dalam sinkronisasi byte kedua (0x53), akan dikirim balik

(echo) ketika mengirimkan byte ketiga dari

instruksi programming enable. Entah

apakah echo ini tepat atau tidak, semua empat byte instruksi ini harus dikirimkan.

|

|

21

Jika 0x53 tidak dikirim balik (echo), beri RESET pulsa positif dan kirim perintah

programming enable yang baru.

4.

Flash diprogram satu page per waktu. Ukuran page bisa ditemukan pada table 2.5

di

bawah. Halaman memory diload per

byte

dengan memberikan 6

LSB

alamat

dan data bersama dengan instruksi Load Program Memory Page. Untuk menjamin

proses

loading page

yang tepat, byte

low pada data harus diload terlebih dahulu

sebelum byte high data diload ke alamat yang diberikan. Program Memory Page

disimpan dengan meload instruksi Write Program Memory Page bersama dengan

8

MSB

alamat.

Jika

polling

tidak

digunakan, user

harus

menunggu

selama

setidaknya

tWD_FLASH

sebelum mengirimkan page berikutnya. Mengakses

interface

programming serial sebelum operasi penulisan Flash selesai dapat

menyebabkan

pemrograman yang tidak tepat.

5.

Array

EEPROM

diprogram perbyte

dengan

cara

mengirim

alamat

dan

data

bersamaan dengan

instruksi

Write

yang diinginkan. Lokasi

memory

EEPROM

pertama-tama akan

dihapus secara otomatis sebelum data

yang baru

ditulis.

Jika

polling

tidak

digunakan, user

harus

menunggu

setidaknya selama

t

WD_EEPROM

sebelum mengirimkan byte berikutnya.

6. Lokasi memory dapat diverifikasi dengan menggunakan instruksi baca yang akan

mengembalikan isi dari alamat yang dipilih pada pin output serial MISO.

7. Pada akhir sesi pemrograman, RESET bisa diset high

untuk melanjutkan operasi

normal.

8. Urutan power – off (jika diperlukan) : Set RESET ke ‘1’kemudian matikan Vcc.

|

r

I

(

START

)

I

Beri deya entara Vee dan Ground

I

!

-

RESET= 0

-

SCK

=

0

-

DP.I Ay 20

ms

I

Klrlm

!'tAriAIprogrami ng AnahiA

I

AVR men g rim balik

Tidak

Ox53?

va

Chi p ArA t'l

AVR tldak

!

terdeteksi

I

Klri

m

serial programing enable

I

I.

Aamat awal

lamat awal

=

0

-

Ld memOt""y low

byte

-

Load memory high byte

-

alamet -++-

va

engi riman s1.1dah

seles a ?

Tidak

I

RESET HIGH

I

Sudeh 1page?

T

va

Tidek

-

WrltA

program mAmory

pagf'l

-

Page++

I

+

(

STOP

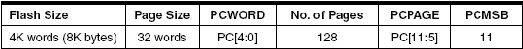

Gambar 2.8 Diagram Alir

algoritma ISP

22

|

23

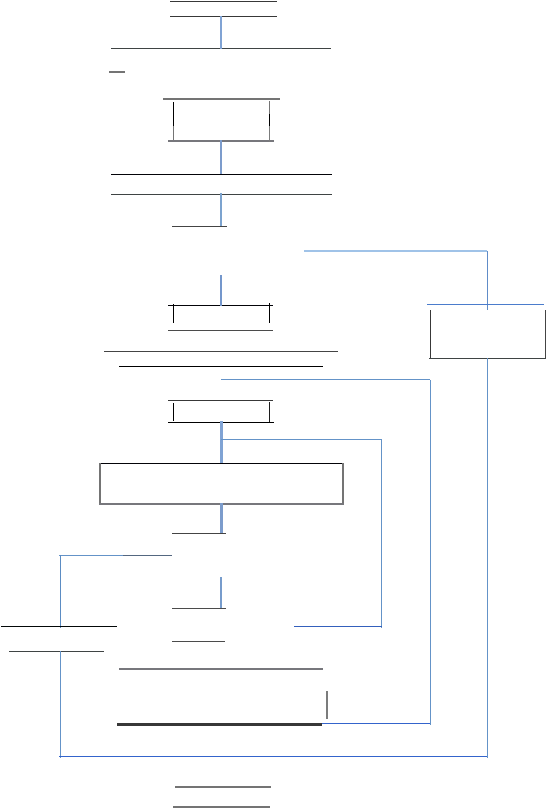

Table 2.5 Jumlah word dalam satu page dan jumlah page dalam Flash

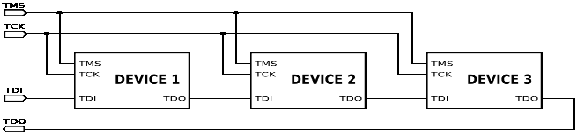

2.5.3 JTAG

JTAG,

singkatan dari

Joint

Test

Action

Group,

adalah

nama

yang

umum

digunakan

untuk

standar IEEE 1149.1

bernama “Standard

Test

Access Port and

Boundary Scan

Architecture”. JTAG distandarisasi tahun 1990 seperti pada IEEE Std.

1149.1-1990.

Pada

1994,

pelengkapnya yang

mengandung

BSDL

(Boundary

Scan

Description

Language)

ditambahkan. Sejak

saat

itu,

standar

ini

telah

diadopsi

oleh

perusahaan elektronik di seluruh dunia. Walaupun awalnya dirancang untuk PCB, JTAG

sekarang

umumnya digunakan

untuk

pengujian IC,

dan

juga

mekanisme

yang

berguna

dalam proses debugging pada embedded system. Module debug yang ada memungkinkan

programmer untuk melakukan debugging software dari sebuah embedded system.

Interface

JTAG

adalah

interface

khusus

dengan

4/5

pin

yang

ditambahkan

ke

chip, didesain sehingga beberapa chip yang terletak di board bisa dihubungkan sekaligus

dengan menggunakan JTAG, dan perangkat penguji rangkaian hanya perlu dihubungkan

ke satu port JTAG untuk bisa mengakses seluruh chip ini. Pin penghubungnya adalah:

1. TDI (Test Data In)

2. TDO (Test Data Out)

3. TCK (Test Clock)

4. TMS (Test Mode Select)

5. TRST (Test ReSeT) yang bersifat optional.

|

24

Gambar 2.9 Contoh rangkaian JTAG

Karena hanya ada satu jalur data tersedia, protokol ini bersifat serial seperti SPI.

Pin

TCK

digunakan

untuk

masukan

clock.

Konfigurasi ini

dilakukan

dengan

memanipulasi satu bit setiap setiap waktu melalui pin TMS. Satu bit data dikirim masuk

dan keluar setiap pulsa clock TCK pada pin TDI dan TDO. Mode instruksi berbeda dapat

digunakan

untuk

membaca

ID

chip,

sample

input

pin,

mengendalikan pin

output,

memanipulasi fungsi chip, ataupun melakukan bypass. Frekuensi operasi TCK berbeda-

beda tergantung pada chip, tetapi umumnya berkisar antara 10-100 MHz.

Ketika

melakukan

boundary

scan

pada

IC,

sinyal

dimanipulasi di

antara

blok

fungsional yang bebeda dari chip, bukannya antara chip yang berbeda. Pin TRST adalah

pin

yang bersifat optional,

merupakan pin reset dengan active

low

untuk

logika

pengujian, biasanya

asinkron, tapi terkadang sinkron, tergantung dari

chipnya.

Jika pin

ini tidak tersedia, logika pengujian bisa direset dengan memberi clock pada instruksi reset

secara sinkron.

2.6

Memori Eksternal AT24C512

AT24C512

terdiri

dari

memory

serial

EEPROM

(Electrically

Erasable

Programmable Read Only Memory) dengan kapasitas memory sebesar 524.288 bit, yang

|

25

tersusun atas 65.536 word masing-masing sebesar 8 bit. Perangkat ini bisa dihubungkan

sampai maksimum 4 buah EEPROM dengan menggunakan bus 2 wire.

Gambar 2.10 Konfigurasi pin AT24C512

Dekripsi fungsi pin :

Serial Clock (SCL) :

Serial Clock input.

Serial Data:

Untuk transfer data serial dua arah.

Alamat device (A1, A0): Pin A1 dan A0 adalah

pin alamat

alat, yang bisa

dihubungkan atau

dibiarkan

tak

tersambung.

Ketika

pin

dihubungkan (hardwire), sebanyak 4 EEPROM

512K

bisa

dihubungkan dalam satu sistem bus tunggal. Ketika pin

ini

tidak disambungkan, nilai default dari A1 dan A0 adalah 0.

Write protect (WP):

Pin untuk perlindungan

penulisan. Jika dihubungkan

ke

ground,

maka

operasi

penulisan normal

bisa

dilakukan.

Ketika dihubungkan dengan

Vcc,

semua

operasi penulisan

ke memory tidak dapat dilakukan.

|

26

AT24C512

tersusun

atas

512

page

masing-masing sebesar

128

byte.

Untuk

pengalamatan wordnya diperlukan alamat sebesar 16 bit.

2.6.1

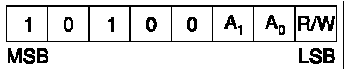

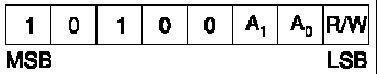

Pengalamatan AT24C512

Pada EEPROM 512K, setelah pengiriman start bit, berikutnya perlu dikirimkan 8

bit

alamat

alat

untuk

memulai operasi

pembacaan ataupun penulisan (lihat

gambar

di

bawah).

Lima

bit pertama

dari

alamat

alat

adalah

10100,

sama

dengan

semua

memory

EEPROM 2 wire lainnya.

EEPROM 512

menggunakan dua bit alamat A1 dan A0 sehingga sebanyak 4 alat

bisa terhubung dalam bus

yang sama. Kedua bit

ini kemudian dibandingkan dengan pin

inputnya.

Bit kedelapan dari alamat alat adalah bit untuk memilih operasi baca/ tulis. Untuk

melakukan operasi baca, bit ini diberi nilai 1, sebaliknya untuk operasi tulis diberi nilai 0.

Gambar 2.11 Device Addressing untuk AT24C512

2.6.2

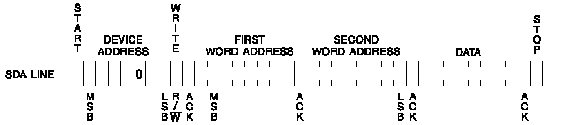

Operasi Penulisan

Penulisan per byte: untuk operasi penulisan, setelah pengiriman alamat alat dan

ACK,

harus

diikuti

dengan

dua

buah

alamat

data 8-bit.

Setelah

menerima alamat

ini,

EEPROM kembali akan membalas dengan mengirim bit 0, dan baru dimulai pengiriman

8-bit data yang pertama. EEPROM kembali akan membalas dengan bit 0. Setelah itu alat

|

27

pengirim,

dalam

hal

ini

adalah

AVR

programmer,

kemudian

harus

mengakhiri proses

penulisan dengan mengirimkan stop bit. Pada waktu ini EEPROM akan memasuki

periode siklus penulisan (t

WR

)

ke memory non volatile. Pada periode penulisan ini semua

input akan dinonaktifkan dan

EEPROM

tidak akan

merespon sampai proses penulisan

selesai.

Gambar 2.12 Urutan operasi penulisan

2.6.3

Operasi Baca

Proses

untuk

mengawali operasi

baca

sama

dengan

operasi

tulis,

hanya

saja

bit

baca/tulis pada alamat alat diset 0. Ada

tiga operasi baca: current address read, random

address read, dan sequential read.

Current address

read:

counter

untuk

alamat

data

internal akan

tetap

mempertahankan nilai

alamat

terakhir

yang

dipakai

untuk operasi baca/

tulis, ditambah

dengan satu. Alamat ini akan tetap bernilai valid selama daya pada chip tidak hilang. Jika

proses pembacaan sudah mencapai alamat byte terakhir pada memory, akan terjadi proses

“roll

over”, dan alamat akan kembali ke

byte pertama. Setelah pengiriman alamat alat,

byte

data

dari

alamat

sekarang

akan

dikirimkan keluar

oleh

EEPROM.

Selanjutnya

mikrokontroler tidak merespon dengan 0, tapi langsung mengirimkan bit stop.

|

28

Gambar 2.13 Urutan operasi baca (current address read)

Random read

:

Untuk operasi pembacaan random read, pertama

harus

dikirim perintah

baca

untuk

mengirimkan alamat word

data.

Setelah

alamat

alat

dan

alamat

word

data

sudah dikirimkan dan EEPROM

mengirimkan ACK, mikrokontroler harus

mengirimkan

perintah

start

bit

berikutnya.

Dengan

begitu

mikrokontroler sekarang

memulai

proses

baca

current

address read

dengan

mengirimkan alamat

alat

dengan bit

baca/

tulis yang

diberi

nilai

1.

Setelah

menerima

alamat

alat

EEPROM

akan

mengirimkan word

data.

Setelah selesai proses pengiriman, dilanjutkan dengan mikrokontroler mengirimkan stop

bit.

Gambar 2.14 Urutan operasi baca (random read)

|