6

•

Penyimpanan banyak instruksi untuk memaksimalkan throuhgput data

•

Eksekusi

secara

kondisional

untuk

semua

instruksi

untuk

memaksimalkan

throughput eksekusi

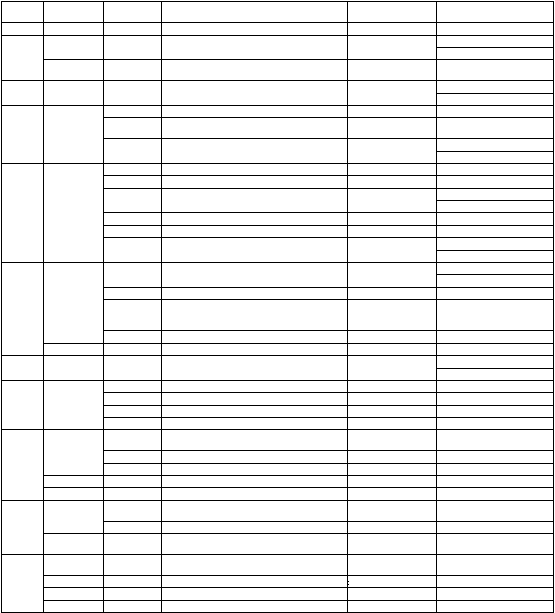

Keluarga

Versi Arsitektur

Inti

Fitur

Cache (I/D)/Memory

management unit

MIPS@MHz

ARM1

ARMv1 (kuno)

ARM1

Tidak ada

ARM2

ARMv2 (kuno)

ARM2

Penambahan instruksi multiply/perkalian (MUL)

Tidak ada

4

MIPS @ 8 MHz

0.33DMIPS/MHz

ARMv2a (kuno)

ARM250

MEMC (MMU), prosesor grafis dan IO terintegrasi.

Menambahkan instruksi SWP and SWPB (swap).

Tidak ada, MEMC1a

7 MIPS @ 12 MHz

ARM3

ARMv2a (kuno)

ARM2a

Pertama kali penggunaan cache.

4 kB unified

12 MIPS @ 25 MHz

0.50 DMIPS/MHz

ARM6

ARMv3 (obsolete)

ARM60

Pertama kali mendukung pengalamatan 32-bit.

Tidak ada

10 MIPS @ 12 MHz

ARM600

Penambahan cache dan coprocessor bus (FPA10 floating-

point unit).

4 kB unified

28 MIPS @ 33 MHz

ARM610

Tidak ada coprocessor bus.

4 kB unified

17 MIPS @ 20 MHz

0.65 DMIPS/MHz

ARM7

ARMv3 (kuno)

ARM700

8 kB unified

40 MHz

ARM710

ARM700

8 kB unified

40 MHz

ARM710a

ARM700

8 kB unified

40 MHz

0.68 DMIPS/MHz

ARM7100

ARM710a, System-on-a-chip.

8 kB unified

18 MHz

ARM7500

ARM710a, SoC.

4 kB unified

40 MHz

ARM7500FE

ARM7500, penambahan FPA dan EDO memory controller.

4 kB unified

56 MHz

0.73 DMIPS/MHz

ARM7TDMI

ARMv4T

ARM7TDMI(-S)

3-stage pipeline, Thumb

Tidak ada

15 MIPS @ 16.8 MHz

63 DMIPS @ 70 MHz

ARM710T

ARM7TDMI, cache

8

kB unified, MMU

36 MIPS @ 40 MHz

ARM720T

ARM7TDMI, cache

8

kB unified, MMU dengan

Fast Context Switch

Extension

60 MIPS @ 59.8 MHz

ARM740T

ARM7TDMI, cache

MPU

ARMv5TEJ

ARM7EJ-S

5-stage pipeline, Thumb, Jazelle DBX, Enhanced DSP

Tidak ada

ARM8

ARMv4

ARM810

5-stage pipeline, static branch prediction, double-bandwidth

memory

8

kB unified, MMU

84 MIPS @ 72 MHz

1.16 DMIPS/MHz

ARM9TDMI

ARMv4T

ARM9TDMI

5-stage pipeline, Thumb

Tidak ada

ARM920T

ARM9TDMI, cache

16 kB/16 kB, MMU

200 MIPS @ 180 MHz

ARM922T

ARM9TDMI, caches

8 kB/8 kB, MMU

ARM940T

As ARM9TDMI, caches

4 kB/4 kB, MPU

ARM9E

ARMv5TE

ARM946E-S

Thumb, Enhanced DSP, cache

variable, tightly coupled

memories, MPU

ARM966E-S

Thumb, Enhanced DSP instructions

no cache, TCMs

ARM968E-S

As ARM966E-S

no cache, TCMs

ARMv5TEJ

ARM926EJ-S

Thumb, Jazelle DBX, Enhanced DSP instructions

variable, TCMs, MMU

220 MIPS @ 200 MHz,

ARMv5TE

ARM996HS

Clockless processor, as ARM966E-S

no caches, TCMs, MPU

ARM10E

ARMv5TE

ARM1020E

6-stage pipeline, Thumb, Enhanced DSP instructions, (VFP)

32 KB/32 KB, MMU

ARM1022E

As ARM1020E

16 KB/16 KB, MMU

ARMv5TEJ

ARM1026EJ-S

Thumb, Jazelle DBX, Enhanced DSP instructions, (VFP)

variable, MMU or MPU

ARM11

ARMv6

ARM1136J(F)-S

8-stage pipeline,SIMD,

Thumb, Jazelle DBX, (VFP), Enhanced

variable, MMU

740 @ 532-665 MHz (i.MX31 SoC),

400-528 MHz

ARMv6T2

ARM1156T2(F)-S

9-stage pipeline,SIMD,

Thumb-2, (VFP), Enhanced DSP instru

variable, MPU

ARMv6KZ

ARM1176JZ(F)-S

As ARM1136EJ(F)-S

variable, MMU+TrustZone

ARMv6K

ARM11 MPCore

As ARM1136EJ(F)-S, 1-4 core SMP

variable, MMU

Tabel 2.1 Versi Arsitektur ARM