36

v

I

LB

0••

STY.JS

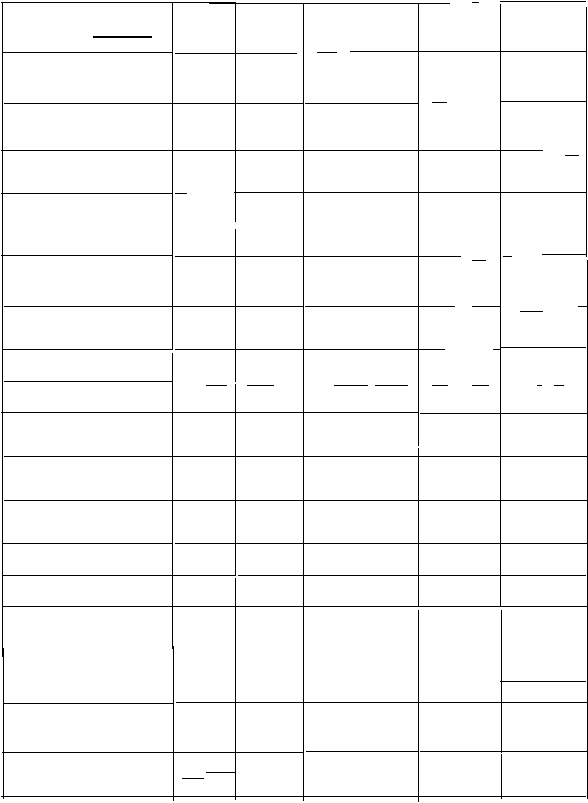

'Iabd 2.4 Ringkasa.n lnstruksi

Perpindahan

Data dari

Lima

Prosesor

dengan

Arsitektur

RJSC

kl;ats. tran;5fer

R-I

R-I

R-I,R-R

R-I,

R-I,R-R

(in§:truction

""'"'"""'J

'

ln.

trnction ruJtme

Alpha

MIPS

l'A-IDSC 2.0

PowerJI>C

SPARC

V9

Load byte signed

i:DBC;

LB

LDB;

LBZ;

LDSB

SEX?B

F:XTRii¹

,

S

31,8

EXTSB

T

;Jcaa

'h

...,

yl

.

e

uns1

•

gno®o

l

LDBU

!LBU

:WliBX,

LDUB

LDBS

Lo:ci halfword

signed

Load

halfword

LDWU;

LDR.;

SEXTW

LH

EXTRW

1

S

LEA

LDSH

3

,16

LD?.:,

L.DHX,

I.DV.TC'

Ll-:f..J

unsigned

LDHS

I,Hz

I..D:TE

Load

word

!.,DLS

LW

LDN,

LDWX,

LW

LD

LLWS

Load SP float

I-DS"

!

LWCl

F:'wD'WX, FI,D?lS

I

LFS

l,DF

Load DP

flc-at

LDT

i

LDC1

FLDDXJ' FLDDS

LF'D

:LDDF

Store

byte

3':3

I

SB

S':'B,

S'TBX 1

.STB

S'I'B

S'l'BS

S'I'H,.

S'l'HXr

S'l'E

STH

Store

halfword

STW

I:!U

S'Y'

S

Store

word

STL

SW

ST'?l,

STWX,

STW

ST

Store

SP float

.

<

..

:::'"

.

L

,...

SWC2.

FSTVlX,

STFS

lsTF

Store DP float

STT

!

SDCl

FSTDX,

FS1DS

STFD

STDF

MFSPR,

RD, w:F..r

Read, vvrite

MF

ME',.-

RD?R,

specia!registers

i

'

M::FCTI:, l"i'I'C'tL

l'!T:::

1-1'1"

-

MTSPR,

1-\TRPR,

li1T

-

LDXFSR..

i

0LH0K

Move

integer

to FP

ITOFS

MI::"'Cl/

STV ';

l?T"t·'""

STW;

s

·

l,DF

register

DMF'Cl

LDFS

"

'

Move FP te

integer

i

b

.l.,lOiS

McCl/

FSTWX;

LDW

S'I'FS;

Ll\

STF;

:LD

p

DMTCl